### **REGULAR PAPERS**

# Analysis of effects of interface-state charges on the electrical characteristics in GaAs/GaN heterojunctions

To cite this article: Shoji Yamajo et al 2018 Jpn. J. Appl. Phys. 57 02BE02

View the article online for updates and enhancements.

## CrossMark

### Analysis of effects of interface-state charges on the electrical characteristics in GaAs/GaN heterojunctions

Shoji Yamajo, Jianbo Liang, and Naoteru Shigekawa\*

Graduate School of Engineering, Osaka City University, Osaka 558-8585, Japan

\*E-mail: shigekawa@elec.eng.osaka-cu.ac.jp

Received June 27, 2017; accepted September 21, 2017; published online December 28, 2017

Electrical properties of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions fabricated by surface-activated bonding are investigated by measuring their capacitance–voltage (C-V) and current–voltage (I-V) characteristics. The difference between their flat-band voltages (0.17 eV), which are extracted from C-V measurements, disagrees with the ideal value (1.52 V), suggesting that the Fermi level should be pinned at the bonding interface. The C-V characteristics of the two junctions are calculated by assuming that the Fermi level is pinned at the interface. The measured C-V characteristics quantitatively agree with modeled ones obtained by assuming that the interface state density and conduction band discontinuity are  $1.5 \times 10^{14}$  cm<sup>-2</sup> eV<sup>-1</sup> and 0.63 eV, respectively. The effective heights of barriers at interfaces, which we estimate by analyzing dependences of I-V characteristics on the ambient temperature, are ~10–20 meV for the two junctions at room temperature. This suggests that the transport of carriers is dominated by tunneling through interface states. © 2018 The Japan Society of Applied Physics

#### 1. Introduction

Gallium nitride (GaN) is a promising component of nextgeneration power devices because of its high breakdown voltage, high thermal conductivity, and the high physical and chemical stabilities.<sup>1,2)</sup> In contrast, GaAs has superior electron transport characteristics and is widely used in highfrequency devices because of its matured growth and process technologies.<sup>3)</sup> Hence, the integration of GaAs and GaN enables us to fabricate unique electron devices for highpower and high-speed applications, which are otherwise unobtainable by either of the single materials. Here, we note that the energy band alignment of GaAs/GaN must be clarified so as to design devices using GaAs/GaN heterojunctions. Several authors reported on the growth of GaAs/ GaN heterojunctions.<sup>4-6)</sup> However, it is still difficult to epitaxially grow GaN layers on GaAs substrates. The quality of epitaxial layers was not satisfactory because of large differences in lattice constants and crystal structure between GaAs and GaN.<sup>7-10)</sup> Furthermore, it was also reported that the nitrogen could diffuse across the GaAs/GaN interface during growth.<sup>11)</sup> The resultant interfacial roughening of the GaAs/ GaN interface together with the high dislocation density and other crystal defects was observed by scanning transmission electron microscope (STEM).<sup>11)</sup>

One way to overcome these difficulties is direct wafer bonding processes such as wafer-fused bonding and surfaceactivated bonding (SAB).<sup>3,12–15)</sup> In wafer bonding, substrates are bonded to each other after surface treatment by chemical agents or fast atom beams. Hence, direct wafer bonding is assumed to enable us to fabricate heterojunctions easily. However, high-temperature annealing is necessary to form junctions in wafer-fused bonding.<sup>16,17)</sup> Such a high-temperature process might cause the degradation of crystal qualities due to the evaporation of arsenic atoms or mechanical defects due to the difference between the thermal expansion coefficients of bonded substrates. In SAB, substrate surfaces are activated by the fast atom beams of Ar prior to bonding without heating. These methods have widely been used for fabricating various junctions, such as Si/Si,<sup>18,19</sup> Si/SiC,<sup>20</sup> GaAs/Si,<sup>21)</sup> and InGaP/Si.<sup>22)</sup> However, it has been reported that interface states with high densities exist at the bonding interface, which is assumed to be due to the formation of interlayers or the imperfection of the interface.<sup>23,24</sup>

Lian et al. fabricated GaAs/GaN p-n heterojunction diodes by wafer-fused bonding and characterized their electrical properties by capacitance-voltage (C-V) and temperaturedependent current-voltage (I-V) measurements.<sup>17)</sup> They presumed that the band alignment was of type II. Kim et al. also reported on GaAs/GaN p-n heterojunction diodes,<sup>3)</sup> which were fabricated by bonding GaAs and GaN substrates to each other after their surfaces were activated by the O<sub>2</sub> plasma. They suggested that the band alignment was of type I. Given that the electron affinities of GaAs and GaN are reportedly 4.07 and 4.1 eV, respectively, their conduction band discontinuity should be  $\sim 0 \,\text{eV}$  in the simplest model. The disagreement in the previously reported two band alignments (type I vs type II), consequently, suggests that a dipole is formed at the GaAs/GaN interface affecting the apparent band alignments. Such a dipole should likely be sensitive to the process of forming the GaAs/GaN interface. The standard model for heterointerfaces<sup>25</sup> predicts that the magnitude of the dipole is sensitive to the charge neutrality level (CNL)<sup>26)</sup> of the adjacent layers. It is also notable that the band bending in each layer depends on the interface charge, or the density of interface states  $(D_{it})$ . The impacts of the interface states on the electrical properties of GaAs/GaN junctions as well as the band alignments, however, have not yet been fully understood.

We previously reported on C-V characteristics of p<sup>+</sup>-GaAs/n-GaN junctions.<sup>27)</sup> In this study, we fabricated p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions by SAB. The electrical properties of the respective junctions were investigated by measuring their C-V and I-V characteristics. We analyzed the effects of charges in the interface states on the C-V characteristics of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions by using the CNL model. The band alignment of the GaAs/GaN interface was estimated from analysis results. Furthermore, the effective barrier heights for the two junctions were estimated using the dependences of their I-V characteristics on the ambient temperature.

#### 2. Experimental methods

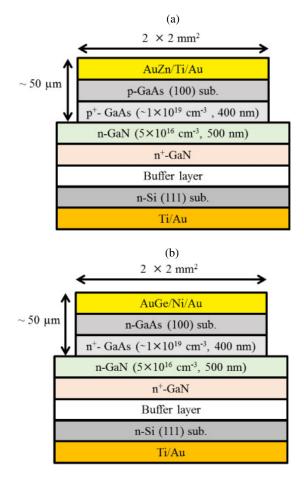

We epitaxially grew p<sup>+</sup>- and n<sup>+</sup>-GaAs layers on p-GaAs(100)

**Fig. 1.** (Color online) Schematic cross sections of GaAs/GaN junctions: (a) p<sup>+</sup>-GaAs/n-GaN and (b) n<sup>+</sup>-GaAs/n-GaN.

and n-GaAs(100) substrates, respectively. The nominal doping concentration and thickness of p<sup>+</sup>- and n<sup>+</sup>-GaAs layers were  $\sim 1 \times 10^{19}$  cm<sup>-3</sup> and 500 nm, respectively. We also prepared an n-GaAs layer epitaxially grown on an n-Si(111) substrate via a buffer layer. The doping concentration and thickness of the n-GaN layer were nominally 5 ×  $10^{16}$  cm<sup>-3</sup> and 400 nm, respectively.

We first formed  $2 \times 2 \text{ mm}^2$  mesas on each of the p<sup>+</sup>- and n<sup>+</sup>-GaAs layers by using a dicer. The height of the mesas was approximately 50 µm. We bonded each of the GaAs substrates to the n-GaN epitaxial substrates by SAB to fabricate p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions. After bonding, GaAs substrates were ground to form  $2 \times 2 \text{ mm}^2$  GaAs/GaN junctions. Contacts on the back side of p-GaAs substrates were formed by evaporating AuZn/Ti/ Au multilayers. Those on the back side of n-GaAs substrates were fabricated by evaporating AuGe/Ni/Au multilayers. Both the p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions were annealed at 400 °C for 60 s in N<sub>2</sub> gas ambient. Then, we evaporated Ti/Au multilayers on the back side of n-Si substrates. The area and thickness of the mesas were  $2 \times$  $2 \text{ mm}^2$  and  $\sim 50 \,\mu\text{m}$ , respectively. The schematic cross sections of the p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions are shown in Fig. 1. Their I-V characteristics were measured with n-GaN grounded at various ambient temperatures between 20 and 200 °C by using the ADCMT 6242 source measurement unit. C-V characteristics were measured with n-GaN grounded at room temperature by using the Agilent E4980A precision impedance analyzer.

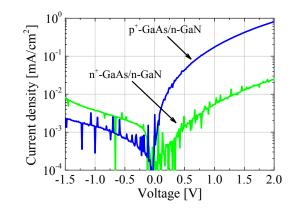

**Fig. 2.** (Color online) *I–V* characteristics of SAB-based GaAs/GaN junctions measured at room temperature.

#### 3. Results

The I-V characteristics of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/ n-GaN junctions are shown in Fig. 2. The curve of p<sup>+</sup>-GaAs/ n-GaN revealed rectifying properties similarly to those of conventional p-n junctions. Although the I-V curve of the n<sup>+</sup>-GaAs/n-GaN heterojunction measured at room temperature showed high leakage currents, the I-V characteristics measured at -50 °C revealed rectifying properties similarly to that of conventional Schottky junctions (not shown here). The reverse-bias current at low reverse bias voltages was sufficiently low to measure C-V characteristics. In addition, we found (not depicted) that the current for forward-bias voltages higher than 8.0 V was almost proportional to the bias voltages in both I-V characteristics, suggesting that the conduction properties in this voltage region were dominated by the parasitic resistance. We estimated the parasitic resistance to be 0.18 and  $5.3 \text{ k}\Omega \text{ cm}^2$  for the p<sup>+</sup>-n and n<sup>+</sup>-n junctions, respectively, from the slope of the curve between 9 and 10 V. The obtained parasitic resistances, which were larger than those in previous report,<sup>3)</sup> are likely due to the high resistivity in buffer layers between the GaN layers and the Si substrates.

The I-V characteristics of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/ n-GaN junctions measured at various temperatures are shown in Figs. 3(a) and 3(b), respectively. The current increased with the bias voltage and temperature in each junction. By extrapolating the current density of each curve to +0 V, we extracted the saturation current density  $(J_0)$  at each temperature. The insets show relationships between the saturation current density divided by the square of the ambient temperature,  $J_0/T^2$ , and q/kT. The slope indicates the barrier heights at bonding interfaces. We fitted each relationship between  $\ln(J_0/T^2)$  and q/kT to a straight line to estimate the barrier heights. The results of fitting are also shown in the insets of Figs. 3(a) and 3(b). Given that each relationship was separated into a high-temperature part with a large slope and a low-temperature part with a small slope, two barrier heights were likely to manifest themselves. The barrier heights for the low-temperature parts were 8 and 19 meV for the p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions, respectively.

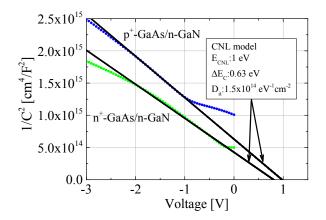

Figure 4 shows the  $1/C^2-V$  characteristics of two junctions measured at a frequency of 2 MHz. Using the slopes of  $1/C^2-V$  characteristics, the donor concentration of

**Fig. 3.** (Color online) Temperature dependences of the *I*–*V* characteristics of (a) p<sup>+</sup>-GaAs/n-GaN and (b) n<sup>+</sup>-GaAs/n-GaN junctions. The inset shows relationships between the saturation current density divided by the square of the ambient temperature,  $J_0/T^2$ , and q/kT.

**Fig. 4.** (Color online) C-V characteristics of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions measured at room temperature and a frequency of 2 MHz.

the n-GaN epitaxial layer was estimated to be approximately  $2.5 \times 10^{16}$  cm<sup>-3</sup> for the p<sup>+</sup>-GaAs/n-GaN junction and  $3.0 \times 10^{16}$  cm<sup>-3</sup> for the n<sup>+</sup>-GaAs/n-GaN junction, which was close to the nominal doping concentration of the n-GaN layer ( $5 \times 10^{16}$  cm<sup>-3</sup>). Although a slight warp was observed in the characteristics, we extracted the flat-band voltage by linearly extrapolating  $1/C^2$  to zero. The flat-band voltage was found to be 0.98 and 0.81 V for p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions, respectively.

The difference in flat-band voltage between p<sup>+</sup>-GaAs/ n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions ( $\Delta V_F$ ) was, consequently, 0.17 V. This value is much smaller than that predicted using the crudest model of the band structures of heterojunctions, which gives

$$\Delta V_{\rm F} = \frac{1}{q} \left( E_{\rm g,GaAs} + \delta_{\rm p-GaAs} + \delta_{\rm n-GaAs} \right)$$

$$\approx \frac{1}{q} E_{\rm g,GaAs} = 1.42 \,\rm V. \tag{1}$$

Note that q is the elementary charge,  $E_{g,GaAs}$  is the band-gap energy of GaAs, and  $\delta_{p-GaAs}$  and  $\delta_{n-GaAs}$  refer to the positions of the Fermi level relative to the valence band maximum in p<sup>+</sup>-GaAs and to the conduction band maximum in n<sup>+</sup>-GaAs, respectively.

#### 4. Discussion

The discrepancy in  $\Delta V_{\rm F}$  between the measurements and the prediction using the crudest model suggested that interface states with high densities were formed at the bonding interfaces and that the Fermi level was pinned. We analyzed the effects of the interface charges on the C-V characteristics of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions by using the CNL model. Here, we assumed the following: (1) The carrier concentrations of the GaAs layers are sufficiently high and their depletion regions are very thin. Consequently, the carriers trapped in the interface states are in thermal equilibrium with those in the GaAs layers, i.e., the Fermi level at the interface coincides with that in the GaAs layers irrespective of bias voltage. (2) The interface states are uniformly distributed in the overlap of band gaps of GaAs and GaN layers. Thereby, their density  $(D_{it})$  is independent of their energy. (3) The distribution of charges in the GaAs layers is locally determined by solving Poisson's equation, and the distribution of charges in the GaN layer is estimated by depletion layer approximation and the space charge in the depletion layer. (4) The sum of charges in the entire junctions is zero.<sup>28)</sup> (5) The CNL of the GaAs side coincides with that of the GaN side, i.e., surface pinning occurs. The CNL of the GaAs side is observed at 1 eV above its valence band maximum  $(E_{\text{CNL}} = 1 \text{ eV},^{29})$  where  $E_{\text{CNL}}$  is the energy of the CNL measured from the valence band edge of GaAs).

For p<sup>+</sup>-GaAs/n-GaN junctions, the density of charges at interface states ( $Q_{it}$ ) can be expressed as

$$Q_{\rm it} = qD_{\rm it} \int_0^{E_{\rm CNL}} [1 - f(E)] \, dE - qD_{\rm it} \int_{E_{\rm CNL}}^{E_{\rm g,GaAs}} f(E) \, dE. \quad (2)$$

The Fermi distribution function f(E) is expressed as

$$f(E) = \frac{1}{\exp\left(\frac{E - E_{\rm f,GaAs}}{kT}\right) + 1},\tag{3}$$

where  $E_{f,GaAs}$  is the Fermi level of the p<sup>+</sup>-GaAs layer, k is the Boltzmann constant, and T is the temperature. Given the surface potential of the p<sup>+</sup>-GaAs layer ( $\varphi_s$ ), the charge density of the p<sup>+</sup>-GaAs layer ( $Q_{p-GaAs}$ ) is expressed as

$$Q_{\text{p-GaAs}} = -\left(4n_{\text{i}}\varepsilon q \left\{\frac{kT}{q} \left[\cosh\left(\frac{q(\varphi_{\text{s}} + \varphi_{\text{B}})}{kT}\right) - \cosh\left(\frac{q\varphi_{\text{B}}}{kT}\right)\right] - \varphi_{\text{s}} \sinh\left(\frac{q\varphi_{\text{B}}}{kT}\right)\right\}\right)^{1/2}$$

(4)

by solving Poisson's equation. In this expression,  $n_i$  is the intrinsic carrier,  $\varepsilon$  is the dielectric constant, and  $\varphi_B$  is the bulk

**Fig. 5.** (Color online) Calculated *C*–*V* characteristics of GaAs/GaN junctions.

potential of GaAs. The charge density of the n-GaN layer  $(Q_{n-GaN})$  is obtained as

$$Q_{\text{n-GaN}} = -(Q_{\text{p-GaAs}} + Q_{\text{it}}) \tag{5}$$

to define the bias voltage. Thus, the relationship between capacitance and bias voltage is numerically calculated by gradually changing  $\varphi_s$ . The *C*–*V* characteristics of the n<sup>+</sup>-GaAs/n-GaN junctions are obtained in similar manners. We formed those equations about  $Q_{n-GaN}$  [Eq. (5)] for p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions. We obtained  $D_{it}$  and  $\Delta E_C$  by simultaneously solving these two equations. We found that the calculated  $1/C^2$ –*V* characteristics obtained by using  $D_{it} = 1.5 \times 10^{14} \text{ cm}^{-2} \text{ eV}^{-1}$  and  $\Delta E_C = 0.63 \text{ eV}$  are in good agreement with the experimental results for both the p<sup>+</sup>–n and n<sup>+</sup>–n junctions, as shown in Fig. 5. We also found that  $D_{it} = 1.5 \times 10^{14} \text{ cm}^{-2} \text{ eV}^{-1}$ , which should be attributed to the irradiation of Ar beams in the SAB process, is as large as those previously reported for GaAs Schottky diodes.<sup>30,31</sup>

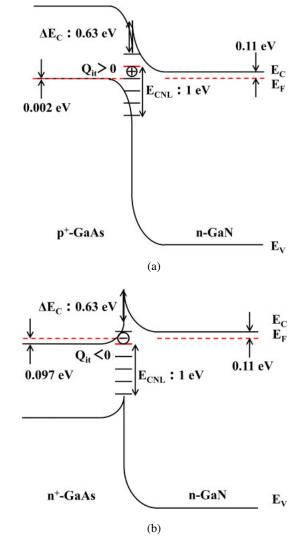

Based on  $E_{\text{CNL}}$ ,  $D_{\text{it}}$ , and  $\Delta E_{\text{C}}$  values, the energy band alignments for p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions in the thermal equilibrium are shown in Figs. 6(a) and 6(b), respectively. The band alignment revealed type I features, which qualitatively agreed with a previous report for GaAs/GaN junctions that were grown by molecular beam epitaxy.<sup>11)</sup> We confirmed that the type I features were obtained by calculation using other  $E_{\text{CNL}}$  values such as  $0.5 \text{ eV}.^{26)}$  Consequently, the band alignment of GaAs/GaN interfaces obtained by the SAB is likely to reveal type I features irrespective of the ambiguity in  $E_{\text{CNL}}$ .

As the temperature increased, the potential barriers became larger, suggesting that the thermionic emission was dominant at higher temperatures. The heights of potential barriers that carriers should overcome at room temperature are 10-20 meV for both the p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions as is shown in the insets of Figs. 3(a) and 3(b), respectively. This suggests that the dominant mechanism of carrier transport across the interfaces is tunneling through the interface states for both junctions. The comparatively large reverse-bias currents observed for the two junctions support this hypothesis. The large difference in parasitic resistance between the p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions, consequently, might be related to the tunneling probabilities of the respective junctions.

Fig. 6. (Color online) Energy band alignments for (a)  $p^+$ -GaAs/n-GaN and (b)  $n^+$ -GaAs/n-GaN junctions.

From the practical viewpoint,  $D_{it}$  such as ~10<sup>14</sup> cm<sup>-2</sup> eV<sup>-1</sup> must be lowered. In the analogy to Si/Si junctions,<sup>23)</sup>  $D_{it}$  is assumed to be lowered by long-period post-bonding annealing. The annealing in the atmosphere in combination with reverse-bias voltages might be useful.<sup>32)</sup> Otherwise, applications with small impacts of interface states such as reversely biased GaAs/GaN junctions should be explored. The type I band alignment suggests that SAB-based GaAs/GaN junctions are potentially applicable to high-voltage devices since high reverse-bias voltages can be applied when ideal interfaces are achieved.

#### 5. Conclusions

We fabricated p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions by surface-activated bonding and examined their electrical properties by measuring capacitance–voltage and current–voltage characteristics. The flat-band voltages of respective junctions deduced from the capacitance–voltage characteristics at 2 MHz were similar (0.98 V: p<sup>+</sup>-GaAs/ n-GaN; 0.81 V: n<sup>+</sup>-GaAs/n-GaN), which was attributed to the pinning of the Fermi level at the bonding interface. The effects of the interface state charges on the *C*–*V* characteristics of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions were analyzed using the CNL model. The modeled *C*–*V*  characteristics were in agreement with the experimental results when the interface state density and conduction band discontinuity were assumed to be  $1.5 \times 10^{14}$  cm<sup>-2</sup> eV<sup>-1</sup> and 0.63 eV, respectively. The band alignment of GaAs/GaN junctions extracted using this model suggested type I features. The dependences of *I*–*V* characteristics on the ambient temperature were analyzed; thus, tunneling through interface states with such a high density was identified as the dominant mechanism of carrier transport across the interfaces of both junctions. Consequently, the difference in parasitic resistance between the p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions might be related to the tunneling probabilities of the respective junctions.

- H. Morkoç, S. Strite, G. B. Gao, M. E. Lin, B. Sverdlov, and M. Burns, J. Appl. Phys. 76, 1363 (1994).

- M. Nozaki, J. Ito, R. Asahara, S. Nakazawa, M. Ishida, T. Ueda, A. Yoshigoe, T. Hosoi, T. Shimura, and H. Watanabe, Appl. Phys. Express 9, 105801 (2016).

- J. Kim, N. G. Toledo, S. Lal, J. Lu, T. E. Buehl, and U. K. Mishra, IEEE Electron Device Lett. 34, 42 (2013).

- 4) K. Wang, D. Pavlidis, and J. Singh, J. Appl. Phys. 80, 1823 (1996).

- S. A. Ding, S. R. Barman, K. Horn, H. Yang, B. Yang, O. Brandt, and K. Ploog, Appl. Phys. Lett. 70, 2407 (1997).

- 6) H. Okumura, S. Misawa, and S. Yoshida, Appl. Phys. Lett. 59, 1058 (1991).

- 7) C. T. Foxon, T. S. Cheng, N. J. Jeffs, J. Dewsnip, L. Flannery, J. W. Orton, I. Harrison, S. V. Novikov, B. Ya. Ber, and Yu. A. Kudriavtsev, J. Cryst. Growth 189–190, 516 (1998).

- A. Trampert, O. Brandt, H. Yang, and K. H. Ploog, Appl. Phys. Lett. 70, 583 (1997).

- N. Kuwano, Y. Nagatomo, K. Kobayashi, K. Oki, S. Miyoshi, H. Yaguchi, K. Onabe, and Y. Shiraki, Jpn. J. Appl. Phys. 33, 18 (1994).

- 10) S. Strite, J. Ruan, Z. Li, A. Salvador, H. Chen, D. J. Smith, W. J. Choyke, and H. Morkoc, J. Vac. Sci. Technol. B 9, 1924 (1991).

- 11) J. Möreke, M. J. Uren, S. V. Novikov, C. T. Foxon, S. H. Vajargah, D. J. Wallis, C. J. Humphreys, S. J. Haigh, A. Al-Khalidi, E. Wasige, I. Thayne, and M. Kuball, J. Appl. Phys. 116, 014502 (2014).

- 12) N. Shigekawa, J. Liang, R. Onitsuka, T. Agui, H. Juso, and T. Takamoto, Jpn. J. Appl. Phys. 54, 08KE03 (2015).

- 13) J. Jasinski, Z. Liliental-Weber, S. Estrada, and E. Hu, Appl. Phys. Lett. 81, 3152 (2002).

- 14) S. Estrada, H. Xing, A. Stonas, A. Huntington, U. Mishra, S. DenBaars, L. Coldren, and E. Hu, Appl. Phys. Lett. 82, 820 (2003).

- 15) H. Takagi, K. Kikuchi, R. Maeda, T. R. Chung, and T. Suga, Appl. Phys. Lett. 68, 2222 (1996).

- 16) Y. C. Zhou, Z. H. Zhu, D. Crouse, and Y. H. Lo, Appl. Phys. Lett. 73, 2337 (1998).

- 17) C. Lian, H. G. Xing, Y. Chang, and N. Fichtenbaum, Appl. Phys. Lett. 93, 112103 (2008).

- 18) J. Liang, T. Miyazaki, M. Morimoto, S. Nishida, and N. Shigekawa, J. Appl. Phys. 114, 183703 (2013).

- 19) H. Takagi, R. Maeda, N. Hosoda, and T. Suga, Jpn. J. Appl. Phys. 38, 1589 (1999).

- 20) S. Nishida, J. Liang, T. Hayashi, M. Arai, and N. Shigekawa, Jpn. J. Appl. Phys. 54, 030210 (2015).

- 21) J. Liang, L. Chai, S. Nishida, M. Morimoto, and N. Shigekawa, Jpn. J. Appl. Phys. 54, 030211 (2015).

- 22) J. Liang, M. Morimoto, S. Nishida, and N. Shigekawa, Phys. Status Solidi C 10, 1644 (2013).

- 23) M. Morimoto, J. Liang, S. Nishida, and N. Shigekawa, Jpn. J. Appl. Phys. 54, 030212 (2015).

- 24) J. Liang, S. Nishida, T. Hayashi, M. Arai, and N. Shigekawa, Appl. Phys. Lett. 105, 151607 (2014).

- 25) J. F. Wager, Thin Solid Films 516, 1755 (2008).

- 26) J. Robertson and B. Falabretti, J. Appl. Phys. 100, 014111 (2006).

- 27) S. Yamajo, J. Liang, and N. Shigekawa, Proc. 5th Int. IEEE Workshop Low Temperature Bonding for 3D Integration, 2017, p. 77.

- 28) N. Shigekawa, J. Liang, M. Morimoto, and S. Nishida, ECS Trans. 64 [5], 235 (2014).

- 29) L. Chai, J. Liang, and N. Shigekawa, Jpn. J. Appl. Phys. 55, 068002 (2016).

- 30) A. M. Cowley and S. M. Sze, J. Appl. Phys. 36, 3212 (1965).

- 31) M. K. Hudait and S. B. Krupanidhi, Mater. Sci. Eng. B 87, 141 (2001).

- 32) S. Kaneki, J. Ohira, S. Toiya, Z. Yatabe, J. T. Asubar, and T. Hashizume, Appl. Phys. Lett. **109**, 162104 (2016).