## Analysis of the influence of interface charges on the electrical characteristics of GaAs/GaN junctions

S. Yamajo, J. Liang, and N. Shigekawa

Graduate School of Engineering, Osaka City University, 3-3-138 Sugimoto, Sumiyoshi-ku, Osaka 558-8585, Japan

*Abstract*— Electrical properties of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN, heterojunctions fabricated by using surface-activated bonding (SAB) are investigated. The measured C-V characteristics of p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN junctions are in quantitative agreement with modeled ones obtained for the interface states density and the conduction-band discontinuity of  $1.5 \times 10^{14}$  cm<sup>-2</sup> eV<sup>-1</sup> and 0.63 eV, respectively.

## I. INTRODUCTION AND BACKGROUND

Gallium nitride (GaN) is promising wide bandgap semiconductors as the next generation power devices because of their high breakdown voltage characteristics. In contrast, GaAs has superior electron mobility and mature growth and process technologies. Hence, the combination of GaN with GaAs enables us to fabricate novel devices targeting both the high-power and high-speed applications with performance not achievable by each component material alone. The GaAs/GaN heterojunctions have been attempted to fabricate in various way. However, it is reported that the interface states with high densities exist at the bonded interface, which is assumed to be due to formation of interlayers or the imperfection of interface[3][4]. In this work, we reported on the electrical properties of GaAs/GaN heterojunctions fabricated by SAB. We examined their electrical properties by capacitance-voltage (C-V) measurements. Furthermore, we analyzed the influence of charges in the interface states on the electrical characteristics of GaAs/GaN junctions by using the charge neutral level (CNL) model[1].

We used two types (p<sup>+</sup>-, n<sup>+</sup>-) of (100) GaAs layers( $\sim 10^{19}$  cm<sup>-3</sup>) epitaxially-grown on GaAs substrates and (0001) n-GaN epi-layers(5×10<sup>16</sup> cm<sup>-3</sup>) grown on Si substrates. We bonded each of GaAs epitaxial substrates to the GaN epitaxial substrates so that p<sup>+</sup>-GaAs/n-GaN and n<sup>+</sup>-GaAs/n-GaN were fabricated. Then we measured the capacitance-voltage characteristics of these samples.

## II. RESULTS

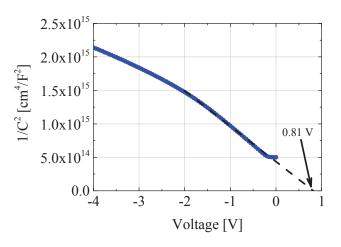

Figure 1 shows the  $1/C^2$ -V characteristics of the n<sup>+</sup>-GaAs/n-GaN junctions measured at room temperature and a frequency of 2 MHz. Using the slopes of  $1/C^2$ -V characteristics, the donor concentrations of the n-GaN epitaxial layer were estimated to be  $3.0 \times 10^{16}$  cm<sup>-3</sup>. Although a slight warp was observed in the characteristics, the flat band voltage V<sub>F</sub> was found to be ~0.81 V by linearly extrapolating  $1/C^2$  to zero. We also obtained that the V<sub>F</sub> of p<sup>+</sup>-GaAs/n-GaN junctions was ~0.98 V by the same way (not shown in this figure). Ideally, the difference V<sub>F</sub> should be approximately the same as the band gap of GaAs. However, that is 0.17 V, which suggests that interface states with high densities are formed at the bonding interfaces and the Fermi level is pinned.

In analyzing the influence of the interface charges on C-V characteristics of GaAs/GaN junctions, we calculated the C-V

characteristics by assuming the energy of CNL ( $E_{CNL}$ ). It was previously reported that  $E_{CNL}$  was located at 0.79–1.00 eV above the valence band edge of GaAs[2]. Although  $E_{CNL}$  had uncertainty to some degree, we used 1.00 eV, which was estimated in the same annealing condition. The calculation results were in good agreement with the experiment data. The obtained interface states density and conduction-band discontinuity were  $1.5 \times 10^{14}$  cm<sup>-2</sup> eV<sup>-1</sup> and 0.63 eV, respectively.

Fig. 1. C-V characteristics of n<sup>+</sup>-GaAs/n-GaN junctions at room temperature.

## REFERENCES

- N. Shigekawa, J. Liang, M. Morimoto, and S. Nishida, ECS Trans. 64 (5) 235 (2014).

- [2] L. Chai, J. Liang, and N. Shigekawa, Jpn. J. Appl. Phys. 55, 068002 (2016).

- [3] J. Kim, N. G. Toledo, S. Lal, J. Lu, T. E. Buehl, and U. K. Mishra, IEEE Electron Device Lett. 34, 42 (2013).

- [4] J. Meoreke, M. J. Uren, S. V. Novikov, C. Thomas Foxon, S. Hosseini Vajargah, D. J. Wallis, C. J. Humphreys, S. J. Haigh, A. Al-Khalidi, E. Wasige, I. Thayne, and Martin Kuball1, J. Appl. Phys. **116**, 014502 (2014)